Power tracking controller design for photo-voltaic systems based on particle swarm optimization technique

Solar energy turns into a promising supply of electricity, so structures of Photo-voltaic (PV) regularly use a maximum power point tracking (MPPT) way to deliver the highest probable power to the load continuously. This paper presents the methodology of PI controller tuning of PV employing Particle Swarm Optimization (PSO). The aim is to obtain the maximum power and maintain its value using the PI controller. It is employed to trace this highest power point value. © 2019 IEEE.

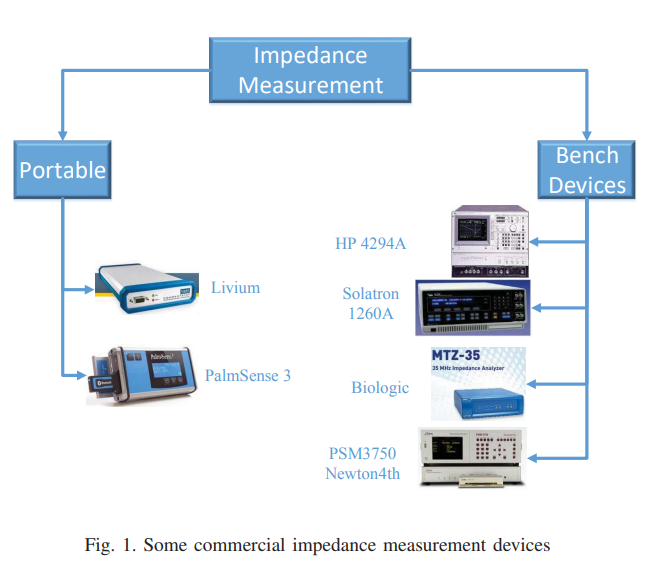

Toward Portable Bio-impedance devices

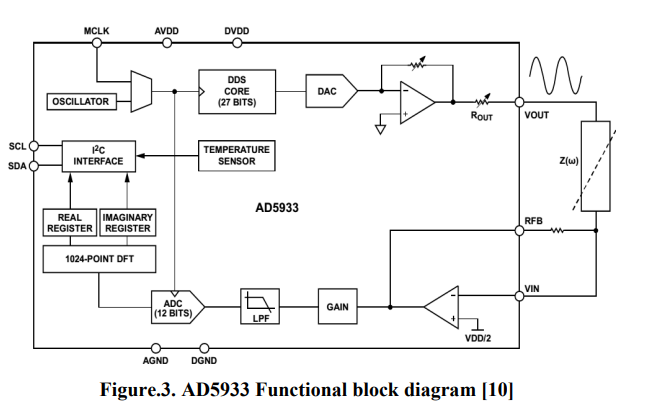

Bio-impedance measurement has been used as an indicator for specific physical and chemical changes in food products, fruits and vegetables, cancer detection and other applications. In this paper, a portable wireless bio-impedance measurement embedded system, based on the AD5933 chip, is introduced. The system is calibrated using a parallel RC network and the industry standard electrochemical station BioLogic SP-150. The module can be used in many impedance measuring applications. © 2019 IEEE.

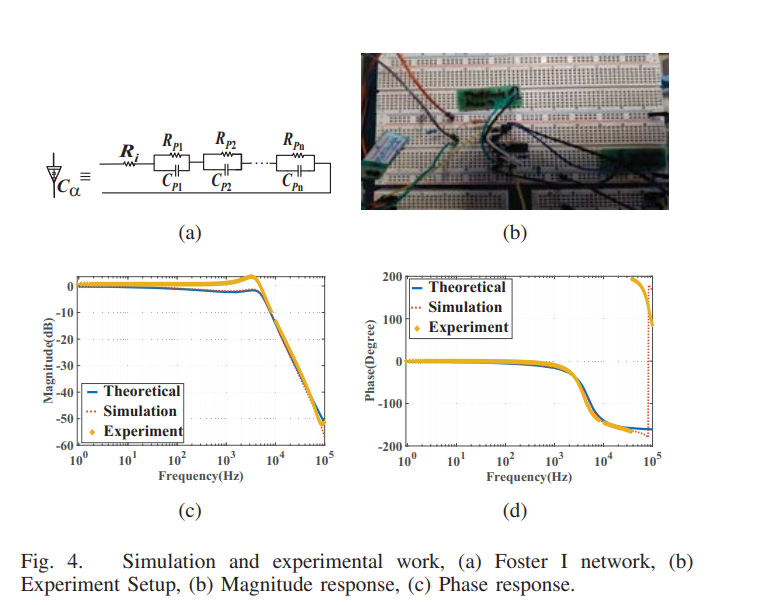

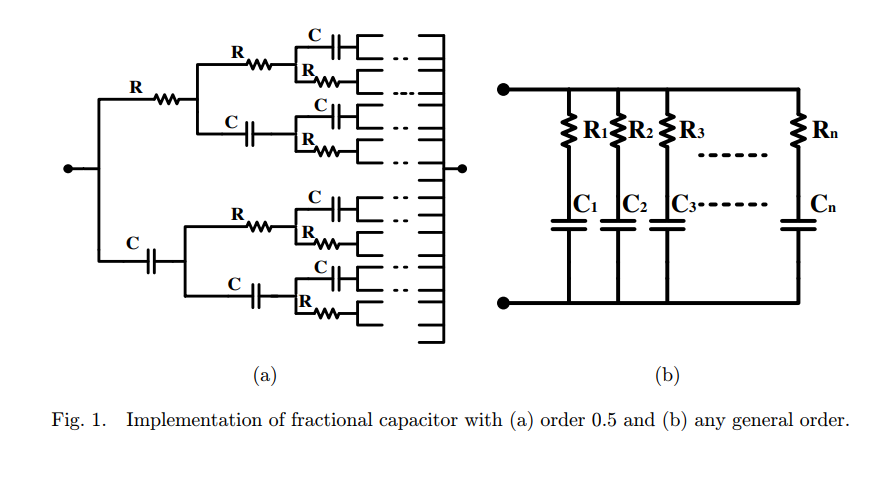

Analysis and Design of Fractional-order Low-pass Filter with Three Elements of Independent Orders

This paper studies a new fractional-order form for the active low-pass filter. The form was mainly generated from generalizing an active second-order low-pass filter with three capacitors to the fractional-order domain with three independent orders. The transfer function introduced an extra term in the denominator comprising the third fractional order. The effect of the third fractional-order alongside the other transfer function coefficients on the critical frequencies had been studied numerically. For simulation purposes, Foster I realization had been utilized to synthesis the fractional

Aging effect on apples bio-impedance using AD5933

In this paper, the effect of the fruits aging on bio-impedance is experimentally studied. Bio-impedance analysis, as accurate and fast method is used to investigate and monitor group of apples properties during aging. This method provides an alternative method for investigating apples physical properties that are highly related to chemical properties. AD5933 impedance analyzer chip within the frequency range (5 KHz-100 KHz) and NI-ELVIS board within the frequency range (300 Hz-5 KHz) are used to investigate the changes in apple's properties during aging. According to experimental results, the

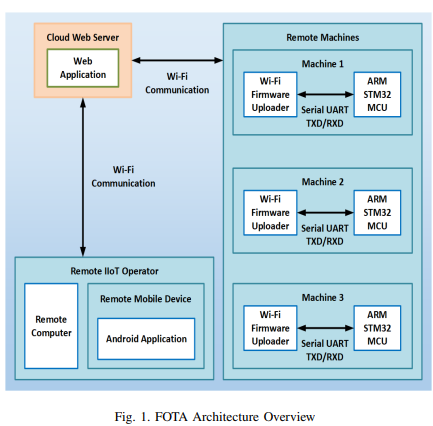

A Scalable Firmware-Over-The-Air Architecture suitable for Industrial IoT Applications

This paper proposes a reliable and scalable architecture for firmware-over-the-air updates, which provides remote cloud real-time distribution of new firmware versions on industrial machines in an efficient simultaneous manner. The architecture comprises remotely interconnected software and hardware systems for handling the procedures of firmware distribution over a wireless network. The main contributions are developing a special boot-loader for ARM micro-controllers and an Android application for performing FOTA updates. A simulation is performed using Web and Android applications showing

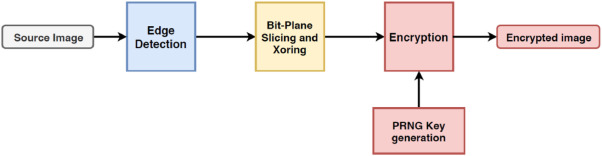

A novel image encryption system merging fractional-order edge detection and generalized chaotic maps

This paper presents a novel lossless image encryption algorithm based on edge detection and generalized chaotic maps for key generation. Generalized chaotic maps, including the fractional-order, the delayed, and the Double-Humped logistic maps, are used to design the pseudo-random number key generator. The generalization parameters add extra degrees of freedom to the system and increase the keyspace achieving more secure keys. Fractional order edge detection filters exhibited better noise robustness than the conventional integer-order ones, rendering the system to be suitable for medical

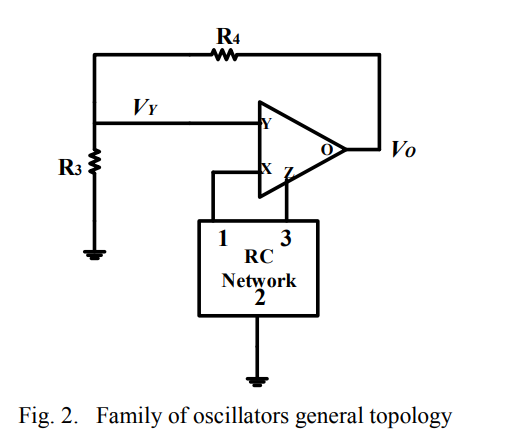

Generalized family of fractional-order oscillators based on single CFOA and RC network

This paper presents a generalized family of fractional-order oscillators based on single CFOA and RC network. Five RC networks are investigated with their general state matrix, and design equations. The general oscillation frequency, condition and the phase difference between the oscillatory outputs are introduced in terms of the fractional order parameters. They add extra degrees of freedom which in turn increase the design flexibility and controllability that is proved numerically. Spice simulations are introduced to validate the theoretical findings. © 2017 IEEE.

Three Fractional-Order-Capacitors-Based Oscillators with Controllable Phase and Frequency

This paper presents a generalization of six well-known quadrature third-order oscillators into the fractional-order domain. The generalization process involves replacement of three integer-order capacitors with fractional-order ones. The employment of fractional-order capacitors allows a complete tunability of oscillator frequency and phase. The presented oscillators are implemented with three active building blocks which are op-Amp, current feedback operational amplifier (CFOA) and second generation current conveyor (CCII). The general state matrix, oscillation frequency and condition are

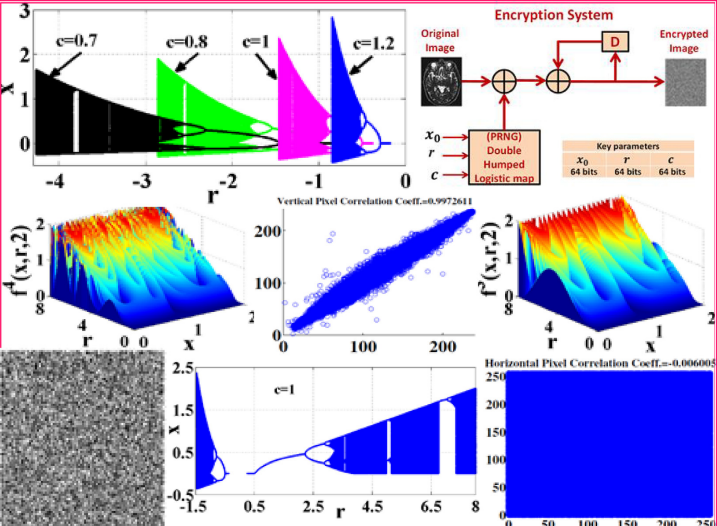

Generalized double-humped logistic map-based medical image encryption

This paper presents the design of the generalized Double Humped (DH) logistic map, used for pseudo-random number key generation (PRNG). The generalized parameter added to the map provides more control on the map chaotic range. A new special map with a zooming effect of the bifurcation diagram is obtained by manipulating the generalization parameter value. The dynamic behavior of the generalized map is analyzed, including the study of the fixed points and stability ranges, Lyapunov exponent, and the complete bifurcation diagram. The option of designing any specific map is made possible through

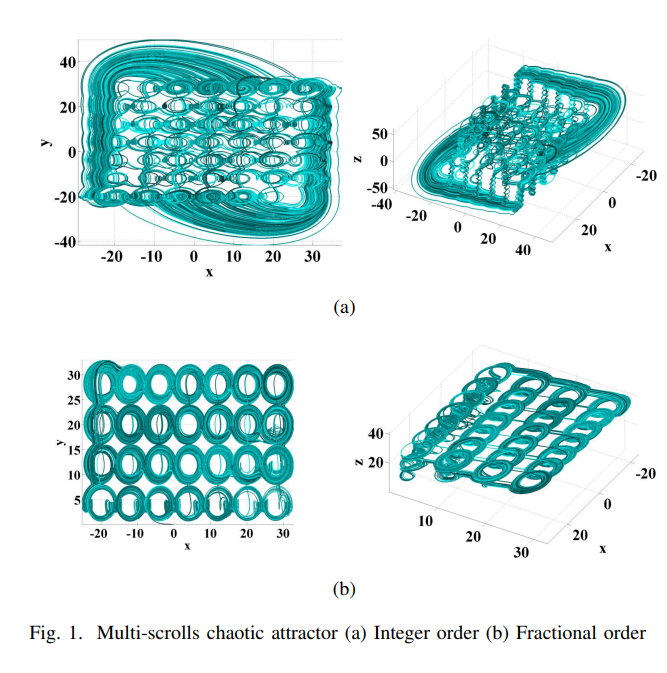

Generic Hardware of Fractional Order Multi-Scrolls Chaotic Generator Based on FPGA

Exploring the implementation of fractional calculus is essential to be adequately used in several applications. This paper introduces an FPGA design methodology of fractional order multi-scrolls chaotic system. Hardware resources comparison proves the efficiency of the proposed method. The designs are simulated using Xilinx ISE 14.7 and realized on FPGA Xilinx Artix 7. Different interesting attractors are realized under various parametric changes with distinct step sizes for different fractional-orders. To verify the proposed fractional order multi-scrolls chaotic system on FPGA, experimental

Pagination

- Previous page ‹‹

- Page 16

- Next page ››