Generalized two-port network based fractional order filters

This paper proposes a general prototype fractional order filter based on a two-port network concept with four external impedances. Three induced classifications from the general prototype are extracted with one, two and three external impedances, achieving ten possible generalized topologies. The external impedances are fractional-order elements and resistors. There are forty-six filters divided into twenty-two and twenty-four different general fractional filters of order “α” and order “α + β”, respectively. The general transfer functions, the necessary network conditions, and the critical

General fractional order mem-elements mutators

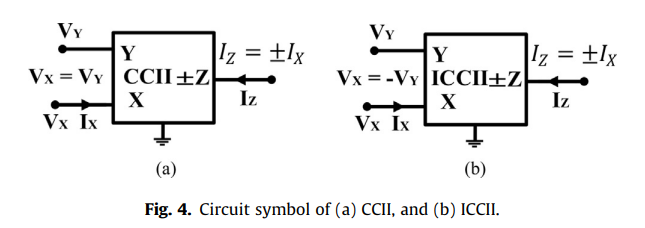

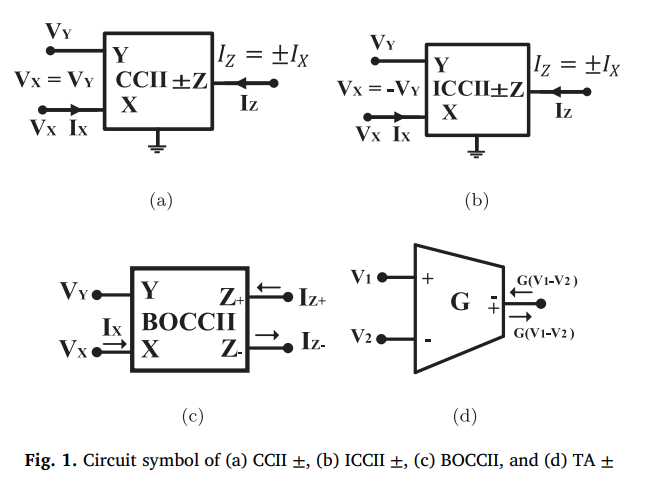

This paper proposes the realization of grounded and floating fractional order mem-elements (FOMEs) based on two- and three-port mutators, respectively. Three different topologies based on two-port mutators are implemented using the four members of the second-generation current conveyor (CCII) family which is useful to achieve several realizations for the same circuit. The Fractional Order Mem-capacitor (FOMC) and Fractional Order Mem-inductor (FOMI) are realized using different combinations of memristor and fractional order capacitor (FOC) plus resistors. In addition, the generalization of the

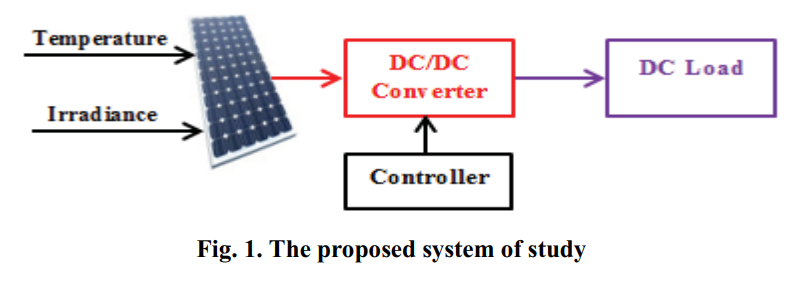

Impact of oustaloup and matsuda approximations on fractional pid controller of pv panel

Due to the non-linear relation between current and voltage of the PV modules, DC/DC power electronic converters are used to adapt this non-linearity. Controllers are used to control the DC/DC converters in order that, they can take actions against changes in irradiance input levels, temperature input levels and load values. In this study, a standalone PV system that feeds a DC load is simulated. Integer order controller and fractional order controller are compared considering two scenarios. The first scenario is to change the irradiance levels while maintaining the load at a constant value. In

Generic FPGA Design of Spiking Neuron Model

This paper introduces a new representation of the human brain neuron cell response. Implementation of a single cell model of an excitatory and inhibitory neuron. The architecture is based on mimic the real reaction of the neuron cell. Excitatory and inhibitory are implemented in generic form for all neuron's behavior. The design is tested experimentally using FPGA. The designs have been realized, simulated using Xilinx ISE 14.7, and realized on Xilinx FPGA Virtex Artix-7 XC7A100T. The proposed realization shows good performance to be compatible with various applications. © 2020 IEEE.

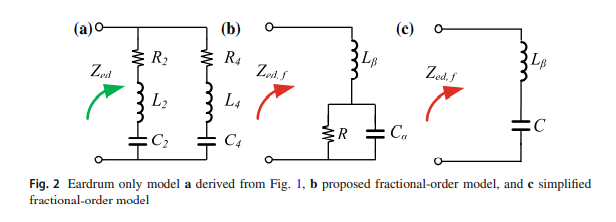

Design and Implementation of an Optimized Artificial Human Eardrum Model

This paper introduces a fractional-order eardrum Type-II model, which is derived using fractional calculus to reduce the number of elements compared to its integer-order counterpart. The proposed fractional-order model parameters are extracted and compared using five meta-heuristic optimization techniques. The CMOS implementation of the model is performed using the Design Kit of the Austria Mikro Systeme (AMS) 0.35 μ m CMOS process, while the simulations have been performed using the Cadence IC design suite. © 2019, Springer Science+Business Media, LLC, part of Springer Nature.

Identifying the Parameters of Cole Impedance Model Using Magnitude Only and Complex Impedance Measurements: A Metaheuristic Optimization Approach

Due to the good correlation between the physiological and pathological conditions of fruits and vegetables and their equivalent Cole impedance model parameters, an accurate and reliable technique for their identification is sought by many researchers since the introduction of the model in early 1940s. The nonlinear least squares (NLS) and its variants are examples of the conventional optimization techniques that are commonly used in literature to tackle this problem based on complex-valued impedance measurement data. However, as happens in most conventional techniques, the NLS and its variants

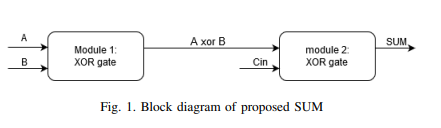

Low Power Scalable Ternary Hybrid Full Adder Realization

Multi-level electronic systems offer speed and area simplicity, reducing the complexity of implementation and power dissipation. In this paper, a Hybrid ternary Full Adder (FA) is proposed using Conventional Complementary Metal Oxide Semiconductor (CCMOS), Double Pass-transistor Logic (DPL), and Pass Transistors (PT). The proposed FA is extended up to 64-bits to test scalability. To validate the proposed full adder and calculate its performance analysis, the Cadence Virtuoso toolset is used at technology 130nm with supply voltage 0.9V. An extra transistor is added to overcome the sneak path

On-the-Fly Parallel Processing IP-Core for Image Blur Detection, Compression, and Chaotic Encryption Based on FPGA

This paper presents a 3 in 1 standalone FPGA system which can perform color image blur detection in parallel with compression and encryption. Both blur detection and compression are based on the 3-level Haar wavelet transform, which is used as a common building block to save the resources. The compression is based on performing the hard thresholding scheme followed by the Run Length Encoding (RLE) technique. The encryption is based on the 128-bit Advanced Encryption Standard (AES), which is considered one of the most secure algorithms. Moreover, the modified Lorenz chaotic system is combined

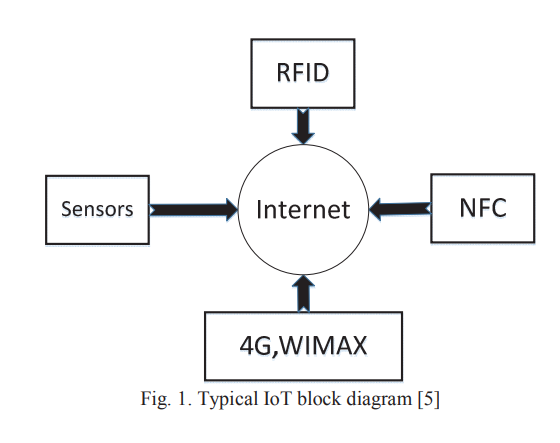

IoT ethics challenges and legal issues

IoT systems have different technologies such as: RIFD, NFC, 3G, 4G, and Sensors. Their function is to transfer very large sensitive and private data. There are many ethical challenges that need to be taken into consideration by individuals and companies that use this technology. Amongst the challenges is the user awareness of attack risks. This paper discusses different ethical and legal challenges that need to be taken in account for IoT health care applications during the near future. © 2017 IEEE.

Fully balanced LED driving circuit for optogenetics stimulation

Implantable probes with built-in light emitters have a promising potential for a range of applications, in particular optogenetic neural stimulation. However, where soft encapsulation methods are used, lifetime will be a function of the quality of encapsulation and the driving mechanism. We have found that a balanced driving mechanism - whereby the integral voltage on encapsulated contacts, can significantly prolong lifetimes. As such, in this work, we have designed a driving circuit that drives current but ensures balanced electric fields with an error of less than 1%. The circuit has been

Pagination

- Previous page ‹‹

- Page 18

- Next page ››