Low Power Scalable Ternary Hybrid Full Adder Realization

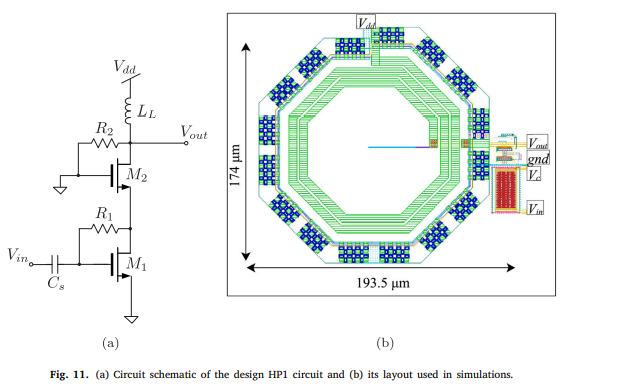

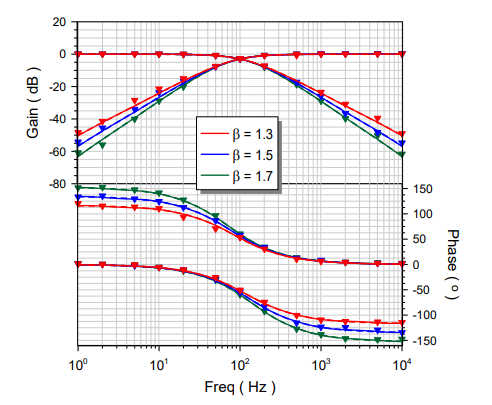

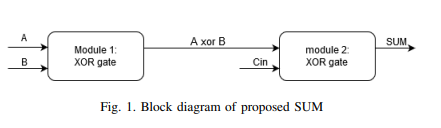

Multi-level electronic systems offer speed and area simplicity, reducing the complexity of implementation and power dissipation. In this paper, a Hybrid ternary Full Adder (FA) is proposed using Conventional Complementary Metal Oxide Semiconductor (CCMOS), Double Pass-transistor Logic (DPL), and Pass Transistors (PT). The proposed FA is extended up to 64-bits to test scalability. To validate the proposed full adder and calculate its performance analysis, the Cadence Virtuoso toolset is used at technology 130nm with supply voltage 0.9V. An extra transistor is added to overcome the sneak path problem that was detected during the simulation. The ternary values 0, 1, and 2 are represented with 0V, 0.45V and 0.9V respectively. According to the simulation results, the proposed work shows a superior performance, which could be considered a promising alternative for low power applications. © 2020 IEEE.