Compact TSV modeling for low power application

[No abstract available]

Behavioral modeling of the static transfer function of ADCs using INL measurements

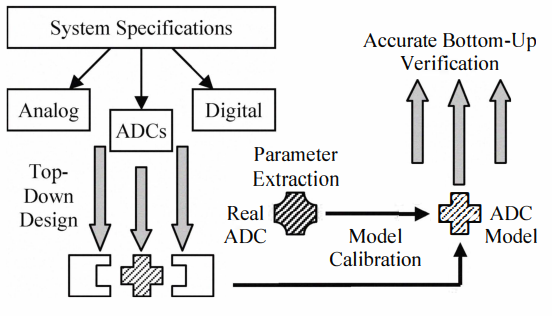

In this paper, we present a modeling approach for analog-to-digital converters (ADCs) based on modeling the static transfer function using integral nonlinearity (INL) measurements. The methodology relies on applying a Fast Fourier Transform (FFT) test to the output of a real ADC circuit and extracting the significant harmonics. These are used in a behavioral functional model to approximate the INL using a polynomial function. The resulting model is independent of the ADC type or structure, and is suitable for bottom-up system verification. We compare the performance of the new model with other

FPAA-based realization of filters with fractional laplace operators of different orders

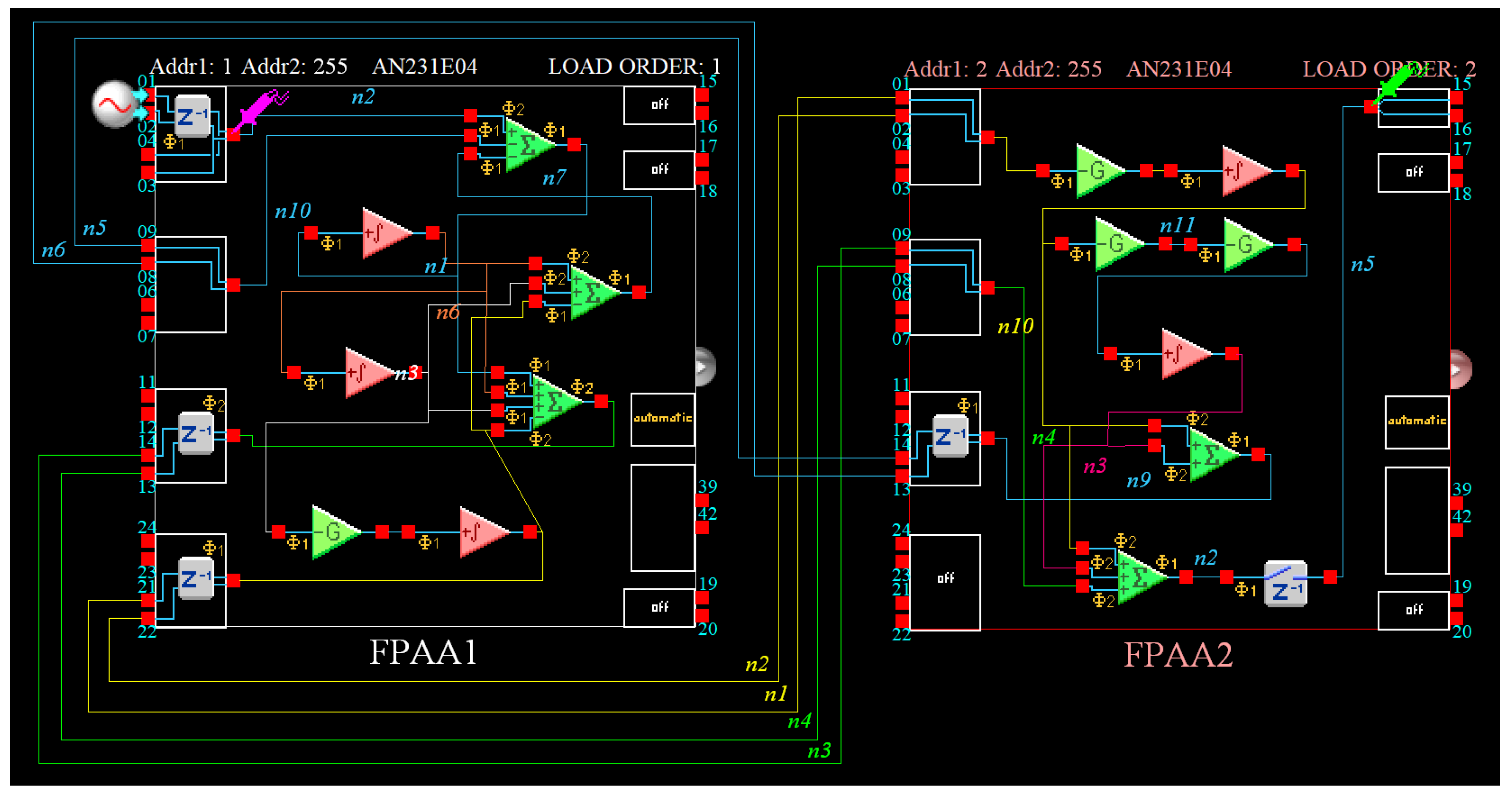

A simple and direct procedure for implementing fractional-order filters with transfer functions that contain Laplace operators of different fractional orders is presented in this work. Based on a general fractional-order transfer function that describes fractional-order low-pass, high-pass, band-pass, band-stop and all-pass filters, the introduced concept deals with the consideration of this function as a whole, with its approximation being performed using a curve-fitting-based technique. Compared to the conventional procedure, where each fractional-order Laplace operator of the transfer

Equivalent lumped element models for various n-port through silicon vias networks

This paper proposes an equivalent lumped element model for various multi-TSV arrangements and introduces closed form expressions for the capacitive, resistive, and inductive coupling between those arrangements. The closed form expressions are in terms of physical dimensions and material properties and are driven based on the dimensional analysis method. The model's compactness and compatibility with SPICE simulators allows the electrical modeling of various TSV arrangements without the need for computationally expensive field-solvers and the fast investigation of a TSV impact on a 3-D circuit

Modeling and characterization of carrier mobility for truncated conical quantum dot infrared photodetectors

In the present paper, a theoretical model for calculating the carrier mobility which is a result of the existence of a truncated conical quantum dots of n-type quantum dot infrared photodetectors (QDIPs) is developed. This model is built on solving Boltzmann’s transport equation that is a complex integro-differential equation describing the carrier transport. The time-domain finite-difference method is used in this numerical solution. The influences of dimensions and density of the QDs for this structure on the carrier mobility are studied. Eventually, the calculated mobility for truncated

Current-Mode Multiplier Accumulator Design using a Memristor-Transistor Crossbar Architecture

This paper discusses the implementation of a Multiplier Accumulator (MAC) design using memristor and crossbar architecture. MAC consists of an array of memristors alongside transistors making a cell that works as a switch (i.e., turned ON or OFF). When a cell is selected, it adds the current in the array path, followed by a current mirror circuit amplified to determine the accumulated current. A traditional MAC is also implemented to compare it with the proposed MAC. The proposed MAC consumed power of 3.9μW, while the traditional MAC consumed power of 19μW. The delay of the proposed MAC is 1

Modeling of Soft Pneumatic Actuators with Different Orientation Angles Using Echo State Networks for Irregular Time Series Data

Modeling of soft robotics systems proves to be an extremely difficult task, due to the large deformation of the soft materials used to make such robots. Reliable and accurate models are necessary for the control task of these soft robots. In this paper, a data-driven approach using machine learning is presented to model the kinematics of Soft Pneumatic Actuators (SPAs). An Echo State Network (ESN) architecture is used to predict the SPA’s tip position in 3 axes. Initially, data from actual 3D printed SPAs is obtained to build a training dataset for the network. Irregularintervals pressure

On numerical approximations of fractional-order spiking neuron models

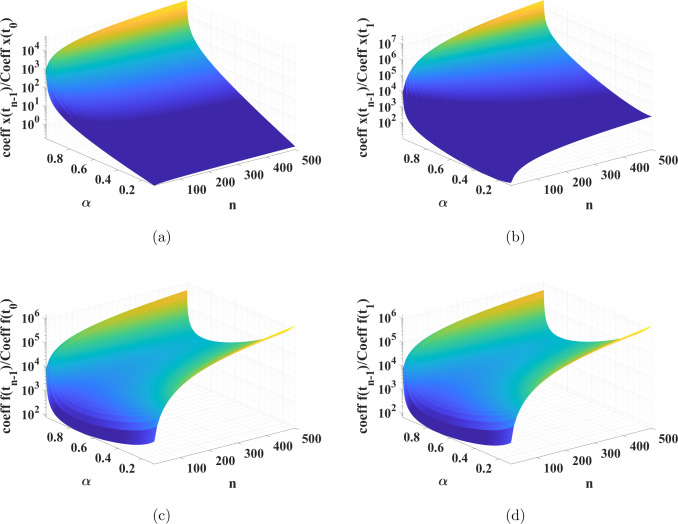

Fractional-order spiking neuron models can enrich model flexibility and dynamics due to the extra degrees of freedom. This paper aims to study the effects of applying four different numerical methods to two fractional-order spiking neuron models: the Fractional-order Leaky integrate-and-fire (FO-LIF) model and the Fractional-order Hodgkin–Huxley (FO-HH) model. Furthermore, some adjustments to these models are proposed, and the effect of reducing the memory size is investigated. We first propose a new realistic formulation for Fo-LIF model to better describe its functionality that is aligned

Fractional-Order and Power-Law Shelving Filters: Analysis and Design Examples

Low-pass and high-pass non-integer order shelving filter designs, which are suitable for acoustic applications, are presented in this work. A first design is based on a standard fractional-order bilinear transfer function, while a second one is based on the transposition of the integer-order transfer function into its power-law counterpart. Both transfer functions are approximated using the Oustaloup approximation tool, while the implementation in the case of the power-law filters is performed through the employment of the concept of driving-point impedance synthesis. An attractive benefit is

Pagination

- Previous page ‹‹

- Page 20

- Next page ››