Generalization of third-order low pass filters to the fractional-order domain with experimental results

This paper is concerned with the generalization of continuous-time 3rd order low-pass filters to the fractional order domain. Three fractional-order capacitors of the same order α are to be considered in the process of filter design. A complete mathematical analysis of the 3rd order fractional low-pass filter is given with stability constraints taken into consideration. Finally, several low-pass active filter design examples are illustrated and discussed in the simulations section in terms of numerical MATLAB simulations, PSpice simulations and experimental results. © 2018 IEEE.

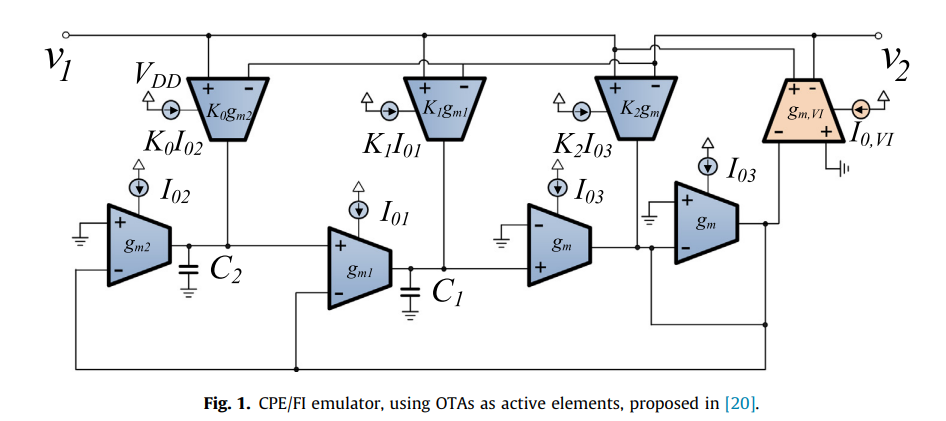

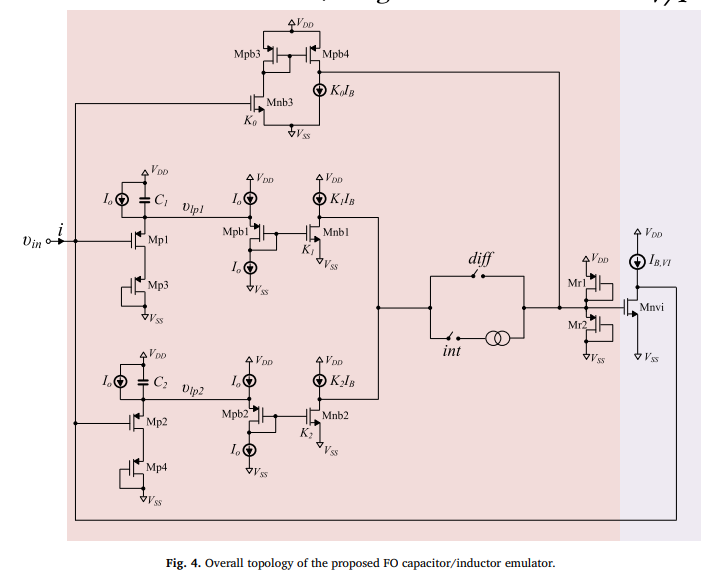

One-terminal electronically controlled fractional-order capacitor and inductor emulator

A novel topology for simultaneous emulation of fractional-order capacitors and inductors is presented in this paper. In particular, only one control terminal is used in order to select the type of the element as well as its fractional order. This is achieved through an appropriate fitting of the expressions of the intermediate bias currents, in such a way that, eventually, only the adjustment of one main bias current is required. The performance of the proposed topology is evaluated through post-layout simulations using Cadence and Austria Mikro Systeme (AMS) 0.35μm CMOS process. © 2019

Low-voltage and low-power fractional-order parallel tunable resonator

A novel implementation of a fractional-order parallel resonator, capable of operating in a ±0.5 V power supply voltage environment, is presented in this work. Compared to the corresponding already published structures, it offers the benefit of reduced circuit complexity, due to the utilization of very simple voltage-mode 1st-order filter sections, leading also to reduction in the dc power consumption. Electronic tuning capability is another attractive feature of the proposed structure achieved using programmable MOS transistor transconductance parameters. © 2019 Elsevier Ltd

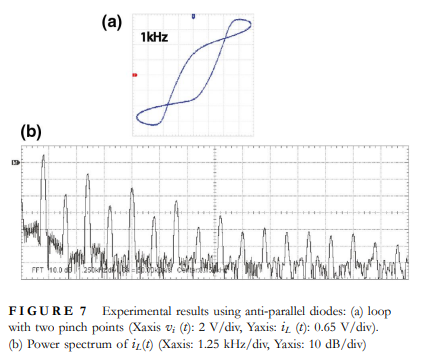

Pinched hysteresis loops in non-linear resonators

This study shows that pinched hysteresis can be observed in simple non-linear resonance circuits containing a single diode that behaves as a voltage-controlled switch. Mathematical models are derived and numerically validated for both series and parallel resonator circuits. The lobe area of the pinched loop is found to increase with increased frequency and multiple pinch points are possible with an odd-symmetrical non-linearity such as a cubic non-linearity. Experiments have been performed to prove the existence of pinched hysteresis with a single diode and with two anti-parallel diodes. The

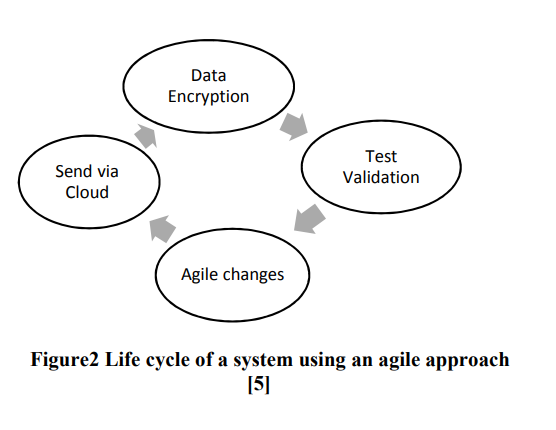

IoT Agile Framework Enhancement

Internet of Things (IoT) is considered as a trend nowadays. Devices connected to the internet interact with surrounding; this poses strong challenges in handling big data with a certain level of security. In this paper IoT devices will be divided in to two categories high vulnerability devices and low vulnerability devices. The classification depends on the ease of attacks. In order to ensure the security of IoT devices, an agile approach is used to secure high vulnerability devices as first step and then low vulnerability devices by applying encryption algorithms. © 2018 IEEE.

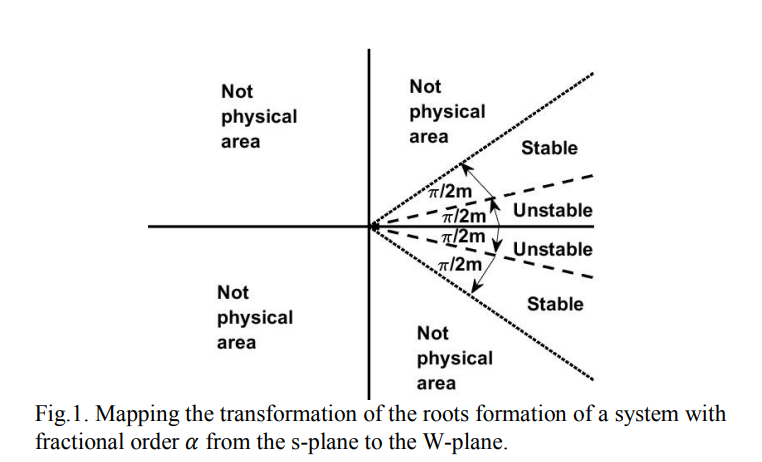

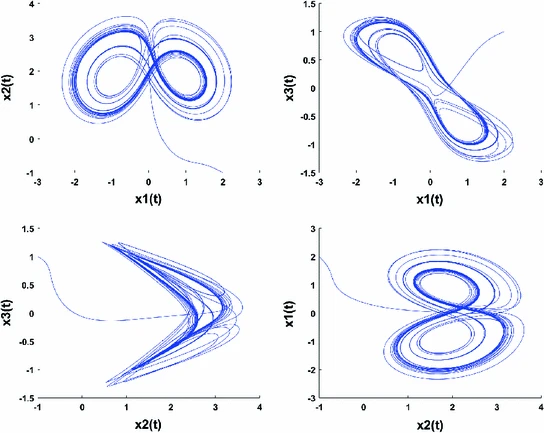

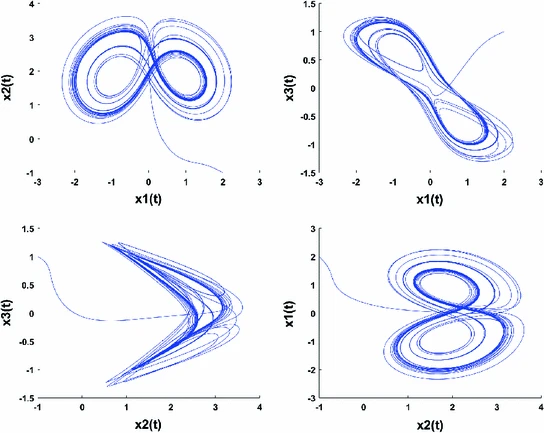

A study on coexistence of different types of synchronization between different dimensional fractional chaotic systems

In this study, robust approaches are proposed to investigate the problem of the coexistence of various types of synchronization between different dimensional fractional chaotic systems. Based on stability theory of linear fractional order systems, the co-existence of full state hybrid function projective synchronization (FSHFPS), inverse generalized synchronization (IGS), inverse full state hybrid projective synchronization (IFSHPS) and generalized synchronization (GS) is demonstrated. Using integer-order Lyapunov stability theory and fractional Lyapunov method, the co-existence of FSHFPS

A study on coexistence of different types of synchronization between different dimensional fractional chaotic systems

In this study, robust approaches are proposed to investigate the problem of the coexistence of various types of synchronization between different dimensional fractional chaotic systems. Based on stability theory of linear fractional order systems, the co-existence of full state hybrid function projective synchronization (FSHFPS), inverse generalized synchronization (IGS), inverse full state hybrid projective synchronization (IFSHPS) and generalized synchronization (GS) is demonstrated. Using integer-order Lyapunov stability theory and fractional Lyapunov method, the co-existence of FSHFPS

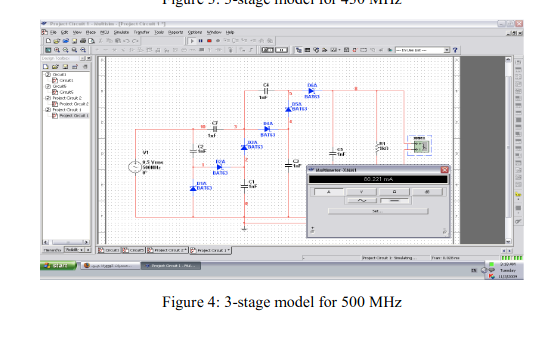

Novel radio frequency energy harvesting model

Energy and Environment, both are the main concern for every researcher allover the world. Alternative energy sources that are environmental friendly became the challenge to satisfy world needs. Oil and Gas are no more the main source of Energy, consequently the demand of an everlasting cheap source of energy that is environmental friendly, is the main goal recently. During the last decade, power consumption has decreased opening the field for energy harvesting to become a real time solution for providing different sources of electrical power. Energy Harvesting is a new technology that is going

Novel permutation measures for image encryption algorithms

This paper proposes two measures for the evaluation of permutation techniques used in image encryption. First, a general mathematical framework for describing the permutation phase used in image encryption is presented. Using this framework, six different permutation techniques, based on chaotic and non-chaotic generators, are described. The two new measures are, then, introduced to evaluate the effectiveness of permutation techniques. These measures are (1) Percentage of Adjacent Pixels Count (PAPC) and (2) Distance Between Adjacent Pixels (DBAP). The proposed measures are used to evaluate

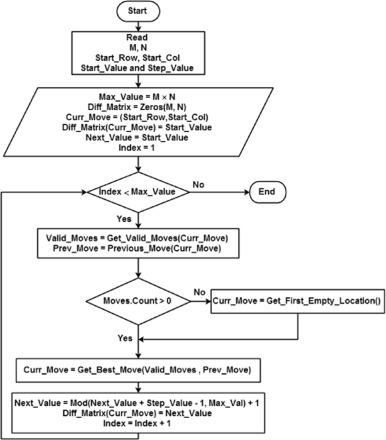

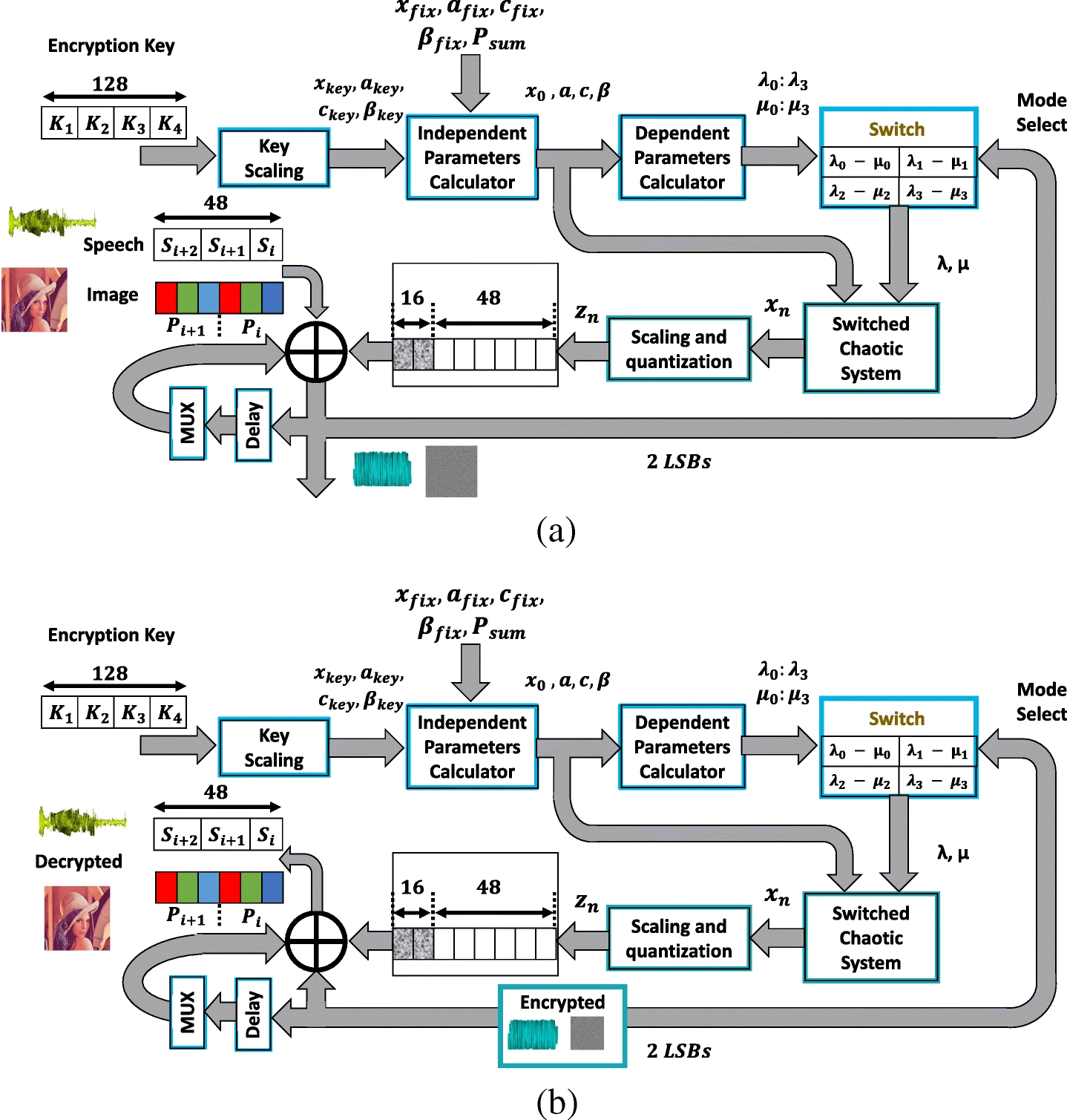

A switched chaotic encryption scheme using multi-mode generalized modified transition map

This paper presents a multi-mode generalized modified transition chaotic map and a switched chaotic encryption scheme based on it. Eight different modes of operation can be selected based on the map graph (concave or convex), the range modification procedure (shrinking or widening) and the sign of one of its independent parameters. The generalization and modification preserve the controllability and continuous chaotic behavior properties, respectively. For the same encryption key and map equation, multi-mode operation occurs through switching between four alternatives of the dependent

Pagination

- Previous page ‹‹

- Page 23

- Next page ››