Feature selection via a novel chaotic crow search algorithm

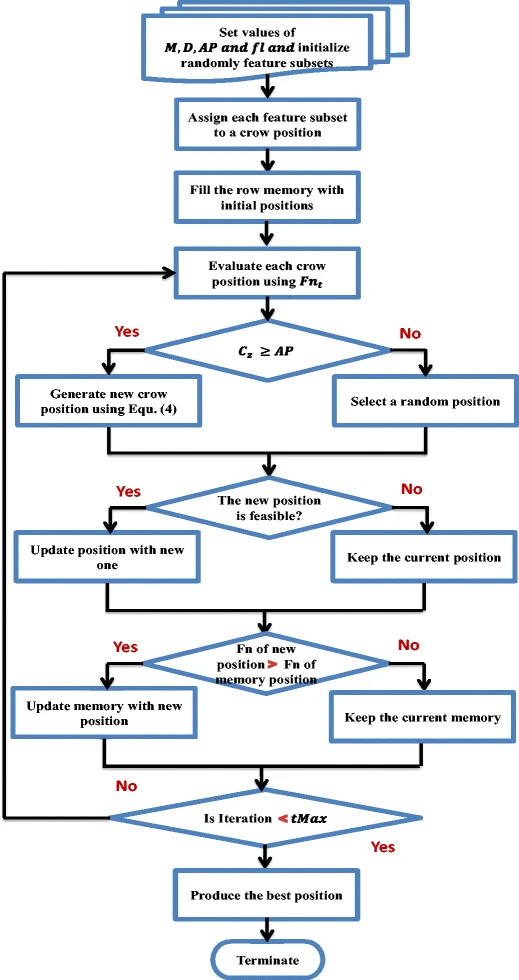

Crow search algorithm (CSA) is a new natural inspired algorithm proposed by Askarzadeh in 2016. The main inspiration of CSA came from crow search mechanism for hiding their food. Like most of the optimization algorithms, CSA suffers from low convergence rate and entrapment in local optima. In this paper, a novel meta-heuristic optimizer, namely chaotic crow search algorithm (CCSA), is proposed to overcome these problems. The proposed CCSA is applied to optimize feature selection problem for 20 benchmark datasets. Ten chaotic maps are employed during the optimization process of CSA. The

Controlled Picard Method for Solving Nonlinear Fractional Reaction–Diffusion Models in Porous Catalysts

This paper discusses the diffusion and reaction behaviors of catalyst pellets in the fractional-order domain as well as the case of nth-order reactions. Two generic models are studied to calculate the concentration of reactant in a porous catalyst in the case of a spherical geometric pellet and a flat-plate particle with different examples. A controlled Picard analytical method is introduced to obtain an approximated solution for these systems in both linear and nonlinear cases. This method can cover a wider range of problems due to the extra auxiliary parameter, which enhances the convergence

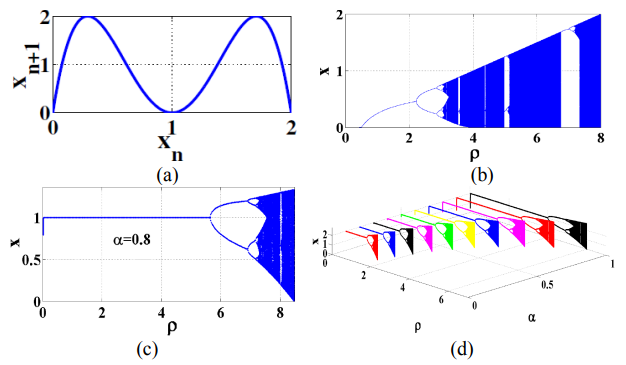

Biomedical image encryption based on double-humped and fractional logistic maps

This paper presents a secured highly sensitive image encryption system suitable for biomedical applications. The pseudo random number generator of the presented system is based on two discrete logistic maps. The employed maps are: the double humped logistic map as well as the fractional order logistic map. The mixing of the map parameters and the initial conditions x0, offers a great variety for constructing more efficient encryption keys. Different analyses are introduced to measure the performance of the proposed encryption system such as: histogram analysis, correlation coefficients, MAE

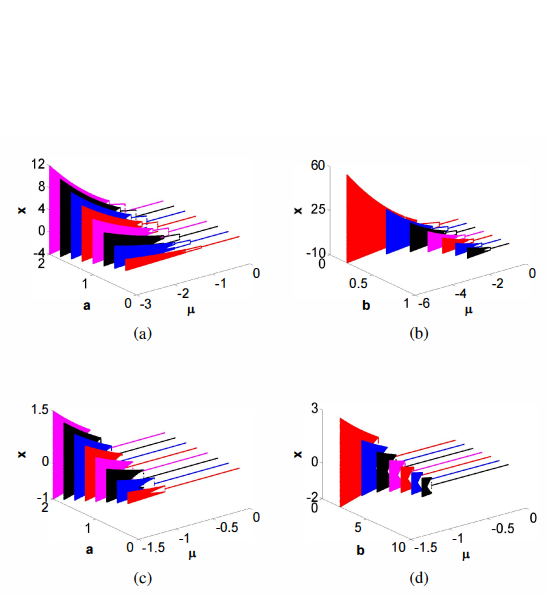

Design of a generalized bidirectional tent map suitable for encryption applications

The discrete tent map is one of the most famous discrete chaotic maps that has widely-spread applications. This paper investigates a set of four generalized tent maps where the conventional map is a special case. The proposed maps have extra degrees of freedom which provide different chaotic characteristics and increase the design flexibility required for many applications. Mathematical analyses for generalized positive and mostly positive tent maps include: bifurcation diagrams relative to all parameters, effective range of parameters, bifurcation points. The maximum Lyapunov exponent (MLE)

Fractional derivative modeling of double-diffusive free convection with von Neumann stability analysis

This paper focuses on the problem of fractional time derivative of fluid flow and convective heat and mass transfer from a heated semi-infinite wall immersed. We provided two cases of study, one is free convective heat transfer and the other is a free double-convective heat and mass transfer. The time-derivative terms in the equations of momentum, energy and concentration are assumed to be fractional using the Grunwald-Letnikov (GL) model. A finite difference scheme has been developed for each case of study and followed by a von Neumann stability analysis. Therefore, a stability condition has

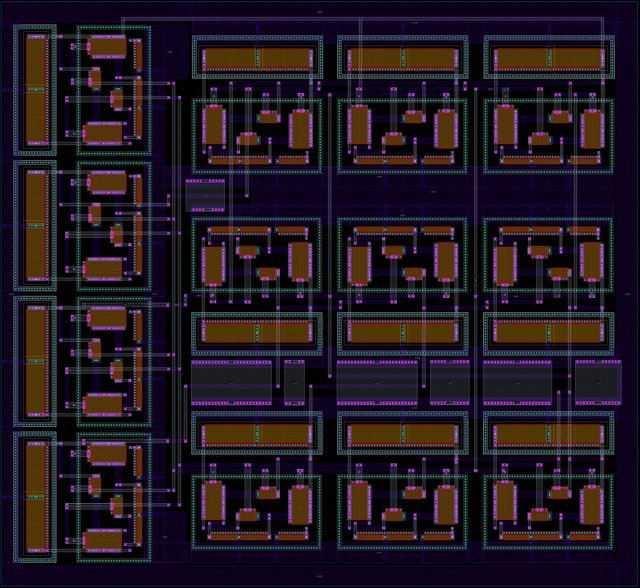

Design of low-voltage FO-[PD] controller for motion systems

Fractional-order controllers have gained significant research interest in various practical applications due to the additional degrees of freedom offered in their tuning process. The main contribution of this work is the analog implementation, for the first time in the literature, of a fractional-order controller with a transfer function that is not directly constructed from terms of the fractional-order Laplacian operator. This is achieved using Padé approximation, and the resulting integer-order transfer function is implemented using operational transconductance amplifiers as active elements

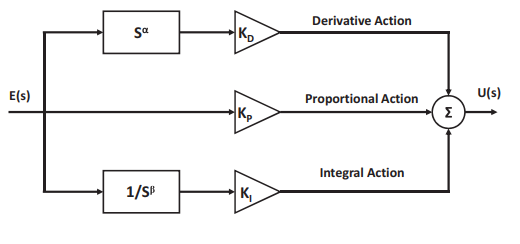

Design of fopid controller for a dc motor using approximation techniques

This paper introduces a study of fractional-order PID (FOPID) controller applied to a DC motor. The idea is to control the motor speed using the FOPID and compare it with the conventional PID controller. Two approximation techniques are employed to realize the FOPID, which are Matsuda and Oustaloup, each with order four. Different responses are depicted for various fractional orders. A specific case study for controlling the speed of a DC motor is investigated with selected fractional-orders. A comparison between the two applied techniques is proposed on the case study to determine which

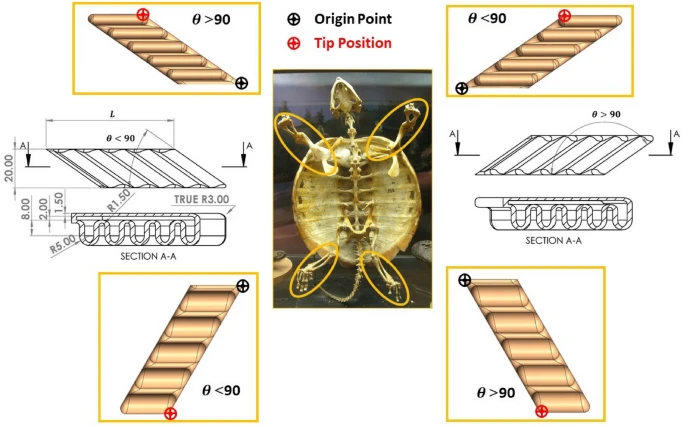

Modelling and implementation of soft bio-mimetic turtle using echo state network and soft pneumatic actuators

Advances of soft robotics enabled better mimicking of biological creatures and closer realization of animals’ motion in the robotics field. The biological creature’s movement has morphology and flexibility that is problematic deportation to a bio-inspired robot. This paper aims to study the ability to mimic turtle motion using a soft pneumatic actuator (SPA) as a turtle flipper limb. SPA’s behavior is simulated using finite element analysis to design turtle flipper at 22 different geometrical configurations, and the simulations are conducted on a large pressure range (0.11–0.4 Mpa). The

Atmospheric pressure air microplasma current time series for true random bit generation

Generating true random bits of high quality at high data rates is usually viewed as a challenging task. To do so, physical sources of entropy with wide bandwidth are required which are able to provide truly random bits and not pseudorandom bits, as it is the case with deterministic algorithms and chaotic systems. In this work we demonstrate a reliable high-speed true random bit generator (TRBG) device based on the unpredictable electrical current time series of atmospheric pressure air microplasma (APAMP). After binarization of the sampled current time series, no further post-processing was

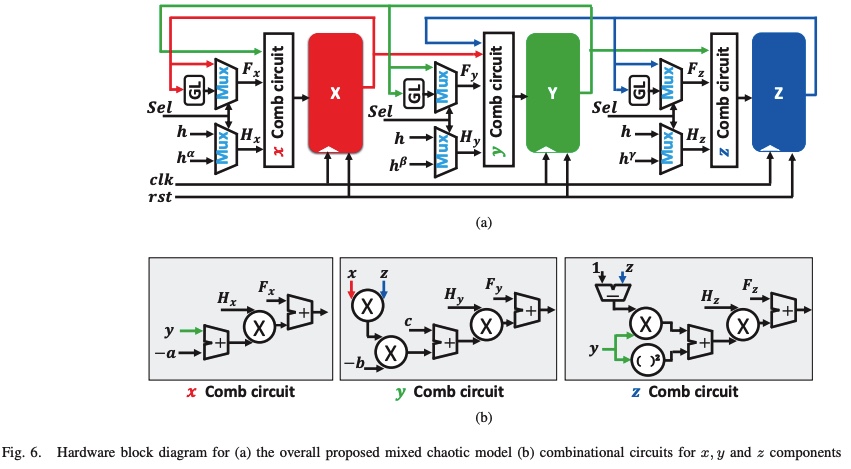

A Digital Hardware Implementation for A new Mixed-Order Nonlinear 3-D Chaotic System

This paper introduces a generic modeling for a 3-D nonlinear chaotic based on fractional-order mathematical rules. Also, a novel modeling for the system using a mixture between integer and fractional-order calculus is proposed. Dynamics of the new realization are illustrated using phase portrait diagrams with complex behavior. Also, a great change in the parameter ranges is investigated using bifurcation diagrams. MATLAB and Xilinx ISE 14.5 are used in system simulations. Furthermore, the digital hardware implementation is done using Xilinx FPGA Virtex-5 kit. The synthesis report shows that

Pagination

- Previous page ‹‹

- Page 24

- Next page ››