Slow-switching-limit loss removal in SC DC-DC converters using adiabatic charging

A novel technique to remove the slow-switching-limit (SSL) loss in switched-capacitor (SC) dc-dc converters is presented. A small series inductor is cascaded with an SC converter causing adiabatic charging of the converter's energy-transfer capacitors. In this work, the theory and necessary conditions for SSL loss elimination through an inductive output filter are derived. The new topology enables high efficiency for on-die dc-dc converters while maintaining reasonable energy density. A 2:1 SC converter is built in 65-nm CMOS process to validate the analysis methods and asses the proposed

A 12Gbps all digital low power SerDes transceiver for on-chip networking

In this paper, a new self-timed signaling technique for reliable low-power on-chip SerDes (Serialization and DeSerialization) links is presented. The transmitter serializes 8 parallel bits at 1.5GHz, and multiplexes the 12Gbps serial data stream with a 24GHz clock on a single line using three level signaling. This new signaling technique enables the receiver to recover the clock from the data with a simple phase detector circuitry. Moreover, this technique is insensitive to jitter accumulated during signal propagation or at the receiver input because the clock signal is extracted from the

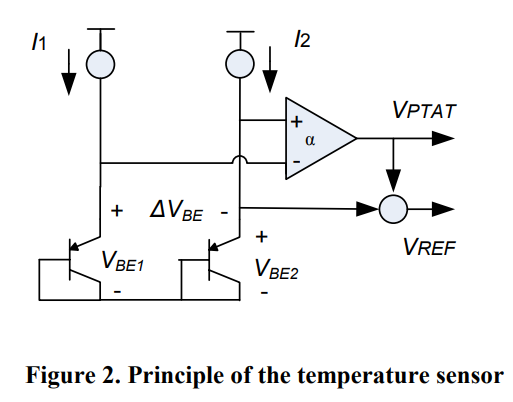

Counter based CMOS temperature sensor for low frequency applications

A simple temperature sensor in Bi-CMOS technology is proposed for applications with low frequency temperature variations in addition to a complete analysis of each block in the system. Most CMOS temperature sensors are based on the temperature characteristics of parasitic bipolar transistors. Two important factors need to be met in the design of the sensor: the first is the accuracy of the sensor, and the second is the power consumption of the temperature sensor that needs to be reduced. A simplified counter approach is used here instead of the commonly used complex decimation filter

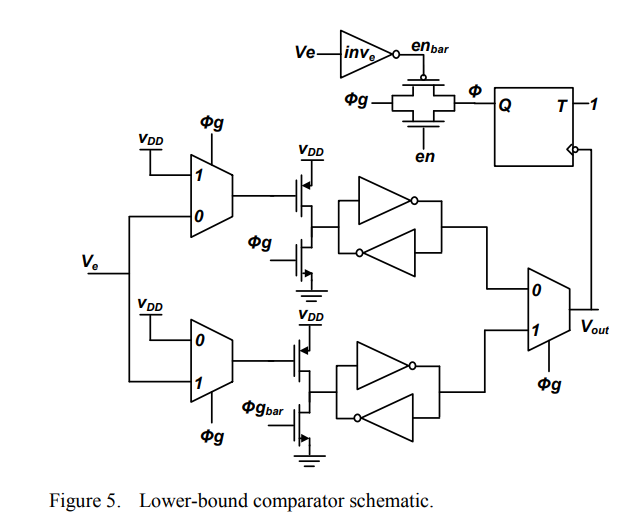

Gain-band self-clocked comparator for DC-DC converters hysteretic control

A novel digital comparator topology is presented. The proposed digital comparator cell uses transistors' ratio to program a fixed comparison level. A double-bound hysteretic control comparator, for DC-DC converters, is built using the proposed digital comparator cell. The hysteretic-band width variation, due to process effects, decreases with increased preamplifier stage gain and constitutes a fixed ratio of the hysteretic-band width. The proposed comparator does not require offset cancellation circuits, which reduces power consumption as well as the die area and increases the comparison speed

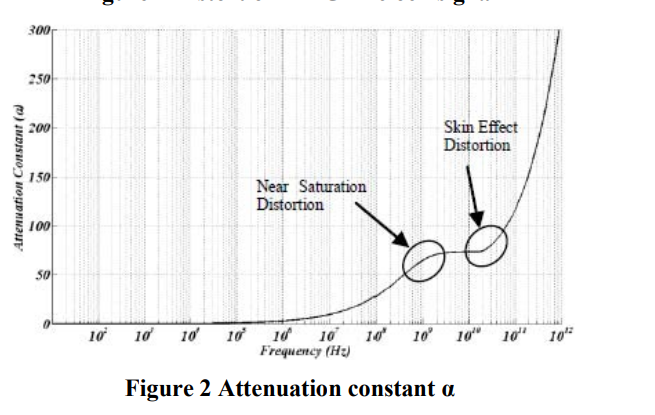

A novel variation insensitive clock distribution methodology

A new clock distribution technique is introduced in this paper. The technique avoids repeaters completely and distributes the clock directly on the passive interconnect network. The wires can be highly lossy, yet the clock is delivered with a very good shape and eye. The technique uses the characteristics of the interconnect to attenuate all frequency components equally. The resulting clock at the sinks does not depend on supply variations at all and only depends on the LC time constant of the wires. Interestingly, the technique works even better with higher clock frequencies. Signal

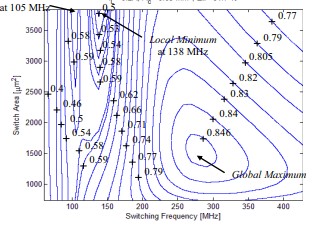

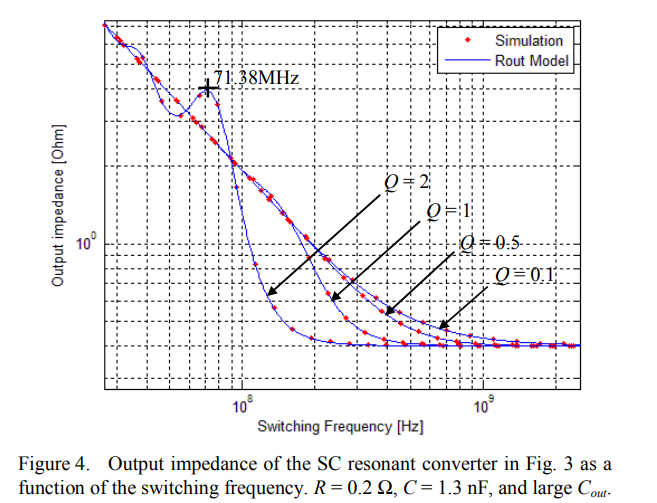

Switched-capacitor dc-dc converters with output inductive filter

Analysis and optimization of switched-capacitor (SC) dc-dc converters with a series inductive filter are developed. The steady-state output impedance of such SC resonant converters is calculated for a 21 conversion ratio. In addition, the necessary conditions for proper application of the output inductive filter are derived. The proposed optimization methodology applies numerical optimization to evaluate different loss components in order to find the optimal design point of highest conversion efficiency. This optimization method is verified through SPICE simulations on a 21 SC power stage in

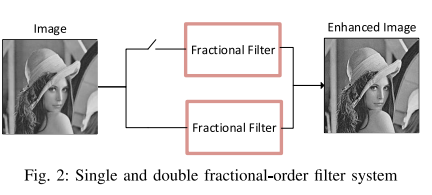

Double Fractional-order Masks Image Enhancement

Image enhancement is better achieved when fractional-order masks are used rather than integer-order ones, this is due to the flexibility of fractional-order parameters control. This paper proposes a combination of fractional-order masks to be used in parallel as double filters system structure to improve image enhancement rather than using a single-stage filter. Various performance metrics are used in this work to evaluate the proposed system, such as Information Entropy (IE), Average Gradient (AG), Structural Similarity Index Metric (SSIM) and Peak Signal to Noise Ratio (PSNR). Based on

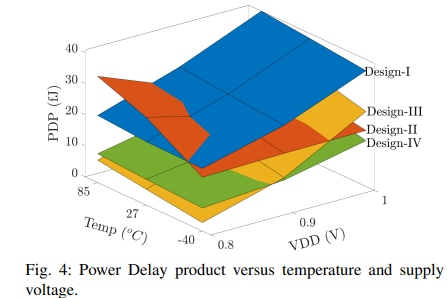

Comparative Study of CNTFET Implementations of 1-trit Multiplier

Ternary logic has become a promising alternative to traditional binary logic due to low power consumption and reduced circuits such as interconnects and chip areas. The efficiency of the multiplier circuit can be much better using a ternary logic system. Carbon nanotube field-effect transistor (CNTFET) is a promising technology as it achieves more advantages than MOSFET due to its low off-current features such as low power and high performance. This paper presents a comparative study of four implementations of a 1-trit multiplier based on CNTFET technology. The comparison is performed in terms

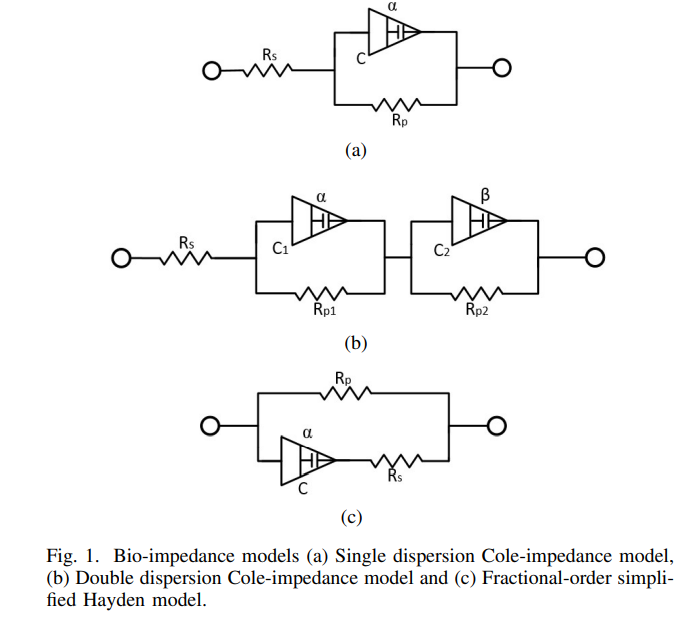

Do the Bio-impedance Models Exhibit Pinched Hysteresis?

Recently, pinched hysteresis has been found in the electrical modelling of regular plant tissues. Usually, the biological tissues are characterized in the frequency domain using bio-impedance analyzers without investigating the time domain, which would show the pinched hysteresis. In this paper, the current-voltage analysis of some of the widely known electrical bio-impedance models is studied. The investigated models are the single dispersion Cole-impedance model, the double dispersion Cole-impedance model and the fractional-order simplified Hayden model to prove that these models can not

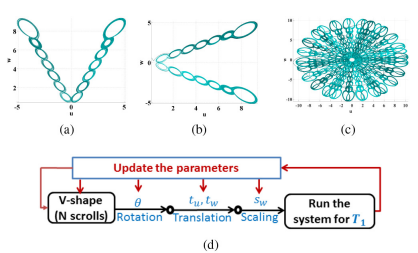

Design and FPGA Verification of Custom-Shaped Chaotic Attractors Using Rotation, Offset Boosting and Amplitude Control

This brief proposes a method of generating custom-shaped attractors, which depends on a planarly rotating V-shape multi-scroll chaotic system with offset boosting and amplitude control, and its FPGA verification. The proposed planarly rotating, translational (offset boostable), and scalable (amplitude controllable) system exhibits a wide basin of attraction and can cover the whole space. Consequently, non-autonomous parameters enable generating attractors of custom-shapes, e.g., letters of the English alphabet as a demonstrating example. Furthermore, non-autonomous parameters are employed to

Pagination

- Previous page ‹‹

- Page 41

- Next page ››