On inverse problem of generalized synchronization between different dimensional integer-order and fractional-order chaotic systems

Chaos is described as a unstable dynamic behavior with dependence on initial conditions. The control and synchronization of chaotic systems requires the knowledge of parameters in advance. Recently researcher's has been shifted from integer order chaotic system to fraction order chaotic system. In this work, based on the stability theory of integer-order linear systems and Lyapunov stability theory, we present some control schemes to achieve a new type of synchronization called inverse generalized synchronization between different dimensional integer and fractional-orders chaotic systems. The

Effect of Different Approximation Techniques on Fractional-Order KHN Filter Design

Having an approximate realization of the fractance device is an essential part of fractional-order filter design and implementation. This encouraged researchers to introduce many approximation techniques of fractional-order elements. In this paper, the fractional-order KHN low-pass and high-pass filters are investigated based on four different approximation techniques: Continued Fraction Expansion, Matsuda, Oustaloup, and Valsa. Fractional-order filter fundamentals are reviewed then a comparison is made between the ideal and actual characteristic of the filter realized with each approximation

Modeling and analysis of fractional order DC-DC converter

Due to the non-idealities of commercial inductors, the demand for a better model that accurately describe their dynamic response is elevated. So, the fractional order models of Buck, Boost and Buck-Boost DC-DC converters are presented in this paper. The detailed analysis is made for the two most common modes of converter operation: Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). Closed form time domain expressions are derived for inductor currents, voltage gain, average current, conduction time and power efficiency where the effect of the fractional order inductor is

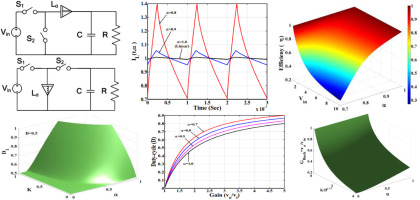

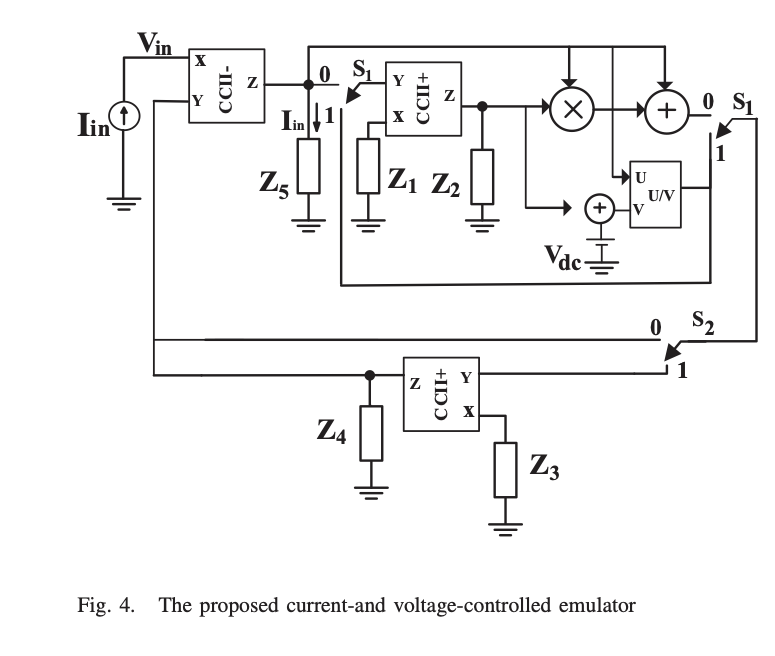

A Universal Fractional-Order Memelement Emulation Circuit

This paper proposes a current-/voltage-controlled universal emulator that can realize any fractional-order memelements (FOME). The proposed emulator consists of second-generation current conveyors (CCII) block, two switches, and a multiplier/divider block. The first switch controls the emulator mode (voltage or current), while, the other controls the type of the emulated FOME. The influence of the fractional-order capacitor (FOC) on the pinched hysteresis loop (PHL) area, is discussed which increases the controllability on the double loop area and the working frequency range. Numerical and

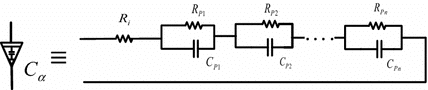

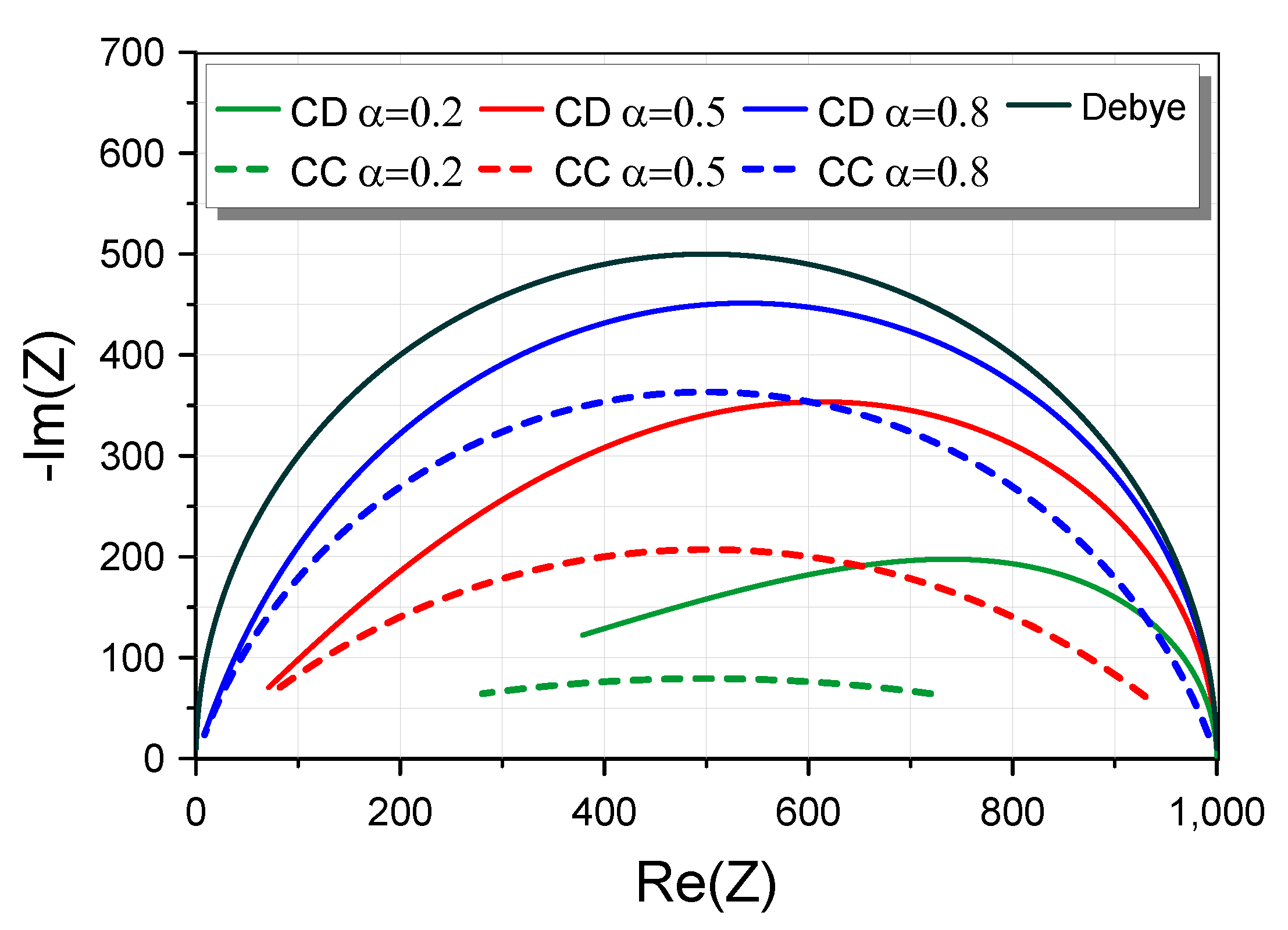

Realization of Cole–Davidson function-based impedance models: Application on plant tissues

The Cole–Davidson function is an efficient tool for describing the tissue behavior, but the conventional methods of approximation are not applicable due the form of this function. In order to overcome this problem, a novel scheme for approximating the Cole–Davidson function, based on the utilization of a curve fitting procedure offered by the MATLAB software, is introduced in this work. The derived rational transfer function is implemented using the conventional Cauer and Foster RC networks. As an application example, the impedance model of the membrane of mesophyll cells is realized, with

Power and energy analysis of fractional-order electrical energy storage devices

Characterizing and modeling electrical energy storage devices is essential for their proper integration in larger systems. However, basic circuit elements, i.e. resistors, inductors, and capacitors, are not well-suited to explain their complex frequency-dependent behaviors. Instead, fractional-order models, which are based on non-integer-order differential equations in the time-domain and include for instance the constant phase element (CPE), are mathematically more fit to this end. Here, the electrical power and energy of fractional-order capacitance and inductance are derived in both steady

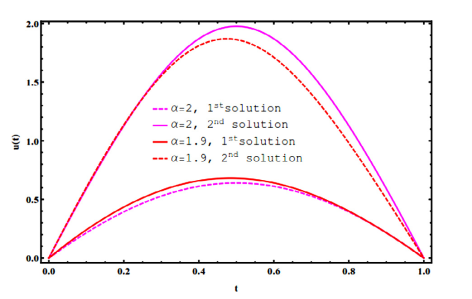

Single and dual solutions of fractional order differential equations based on controlled Picard's method with Simpson rule

This paper presents a semi-analytical method for solving fractional differential equations with strong terms like (exp, sin, cos,…). An auxiliary parameter is introduced into the well-known Picard's method and so called controlled Picard's method. The proposed approach is based on a combination of controlled Picard's method with Simpson rule. This approach can cover a wider range of integer and fractional orders differential equations due to the extra auxiliary parameter which enhances the convergence and is suitable for higher order differential equations. The proposed approach can be

Modeling of carrier mobility for semispherical quantum dot infrared photodetectors (QDIPs)

Carrier mobility for quantum dot infrared photodetectors is considered as one of the critical parameters to determine many important device’s performance parameters such as the electrical conductivity, drift velocity, dark current and photocurrent. In this paper a complete theoretical model of the carrier mobility for semispherical quantum dot structures is developed. This model is based on the solution of Boltzmann transport equation all over the device. A parametric study of the effects of the QD density and the dimensions of the QD on the carrier mobility is investigated. Finally, the

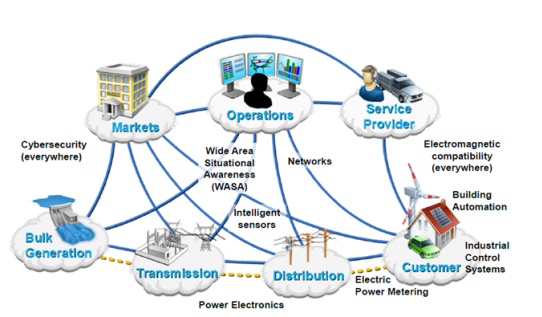

Energy Trading Based on Smart Contract Blockchain Application

Energy and clean energy are big concerns and interests. As the needs differ from area to another, different solutions appear. Energy cost, availability, reliability and trading rules are important keys in energy market. Energy sharing is a hot topic as a consumer being a part of the sustainable distributed system also making benefits such as Prosumer. Blockchain technology provides more secure, distributed and fast way to transact financial payments between clients. This paper provide a simulation case for energy sharing concept using smart contract as a tool to rule the sharing process on

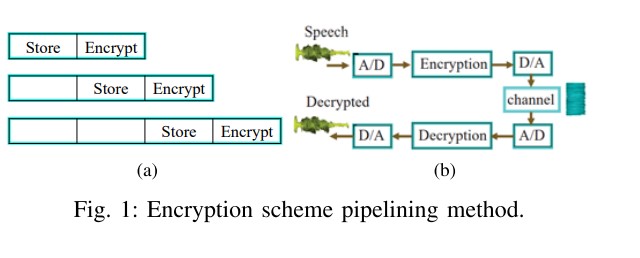

Permutation-Only FPGA Realization of Real-Time Speech Encryption

This paper introduces an FPGA design methodology of a sample and bit permutation speech encryption system. Pipelining method is used to build the proposed system, which can have different number of permutation levels. The security of the system is evaluated using entropy, Mean Squared Error (MSE) and correlation coefficients comparing the different permutation levels. The results demonstrate the security of the proposed system, which enables its utilization in speech telecommunication. Hardware resources comparison validates the efficiency of the system. The designs are simulated using Xilinx

Pagination

- Previous page ‹‹

- Page 42

- Next page ››