Utilization of Machine Learning In RTL-GL Signals Correlation

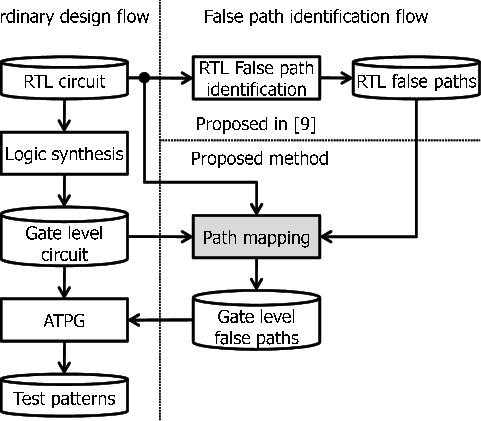

Verification is an important part of the Electronic Design Automation (EDA) design flow which currently takes a considerable amount of time. During the synthesis process, Different optimizations are done to the Register-Transfer-Level (RTL) code to optimize the power, area, and speed of the circuit. These optimizations result in changes in the names of signals at the gate level. Automatic signal mapping can improve the verification process and can be used to guide functional verification activities between the two presentations using (Clock domain crossing (CDC) analysis in RTL, Gate Level CDC) as well as Formal Sequential Equivalence Checking. Machine Learning has applications everywhere in our lives, and EDA is not an exception. Machine Learning can help EDA tools optimize their results by learning from their previous choices which would improve their results. Machine Learning can help in decreasing the amount of time used in the verification process and increase productivity. In this paper, we discuss the methods used in the signal correlation, propose a modification to one of them as well as present a new technique using Machine Learning to solve the problem of signal correlation between the RTL and the gate level. © 2021 IEEE