A fast locking hybrid TDC-BB ADPLL utilizing proportional derivative digital loop filter and power gated DCO

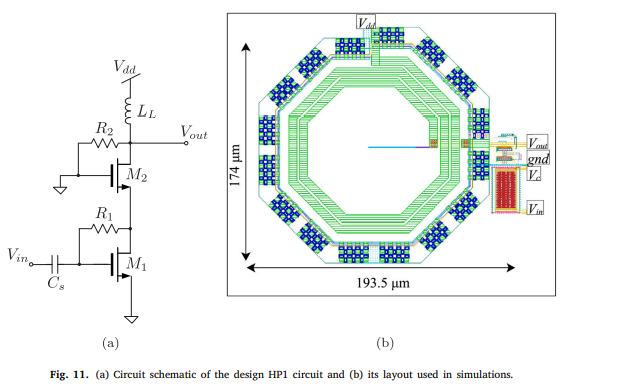

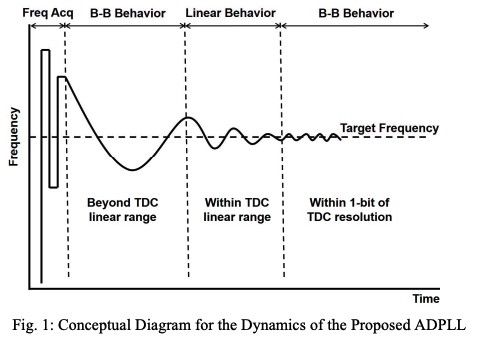

A hybrid Time to Digital Converter (TDC) - Bang Bang (BB) All Digital Phase Locked Loop (ADPLL) architecture is proposed to optimize power, area, lock time, and design complexity. The Hybrid ADPLL architecture utilizes a low resolution two synthesizable Time to Digital Converters to achieve fast lock time, and then switches to a Bang-Bang like architecture once it is in the locked state. Such hybrid architecture enables the ADPLL to achieve lock time in less than 1 μ sec using an adaptive proportional derivative digital loop filter while consuming a power of 5.1 mW when locked at 4GHz with 1.37 ps rms period jitter. Additionally, The proposed ADPLL utilizes a novel power gated digitally controlled oscillator to power minimum number of transistors once the ADPLL is locked in a specific frequency band. The ADPLL occupies a total area of 85×150 μm2 when synthesized on TSMC 65nm. © 2016 IEEE.