An Ultra-Low Power Wide-Band Single-Transistor Second-Order Allpass Filter in 65nm CMOS

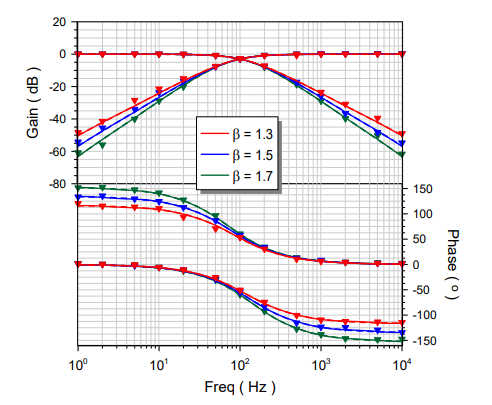

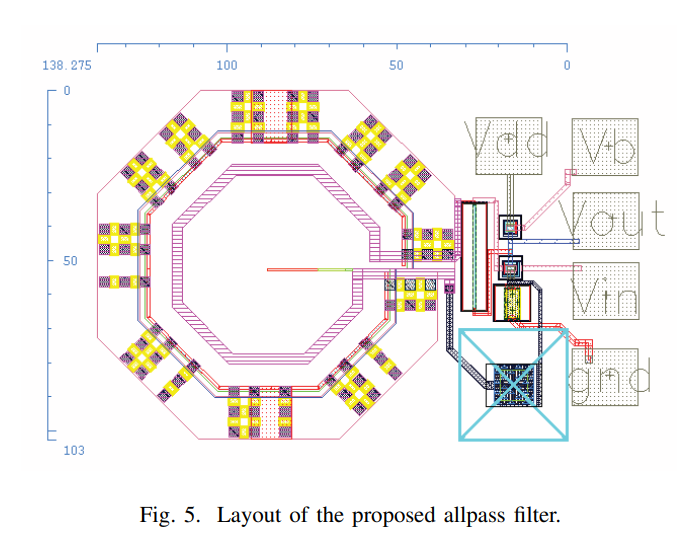

In this paper, we propose a MOS design of a second-order voltage-mode allpass filter to be used as a time delay cell. The proposed filter is based on a single transistor, three resistors and two energy storage elements and was designed in a 65nm CMOS technology. Post-layout simulations demonstrate a group delay of approximately 13ps across a 30GHz bandwidth, while only consuming 809.7μW from a 1-V supply. As a proof of concept, the proposed filter was constructed and verified experimentally using discrete MOS transistors. The experimental results show a group delay of approximately 370ns across a 1.22MHz bandwidth. © 2019 IEEE.