Memristive Bio-Impedance Modeling of Fruits and Vegetables

Recent works show that the plants can exhibit nonlinear memristive behavior when excited with low-frequency signals. However, in the literature, only linear bio-impedance models are extensively considered to model the electrical properties of biological tissues without acknowledging the nonlinear behavior. In this paper, we show with experiments, for the first time, the pinched hysteresis behavior in seven fruits and vegetables including tomato, orange, lemon, aubergine, and kiwi which exhibit single pinch-off point, and others such as carrot and cucumber exhibit double pinch-off points (i.e

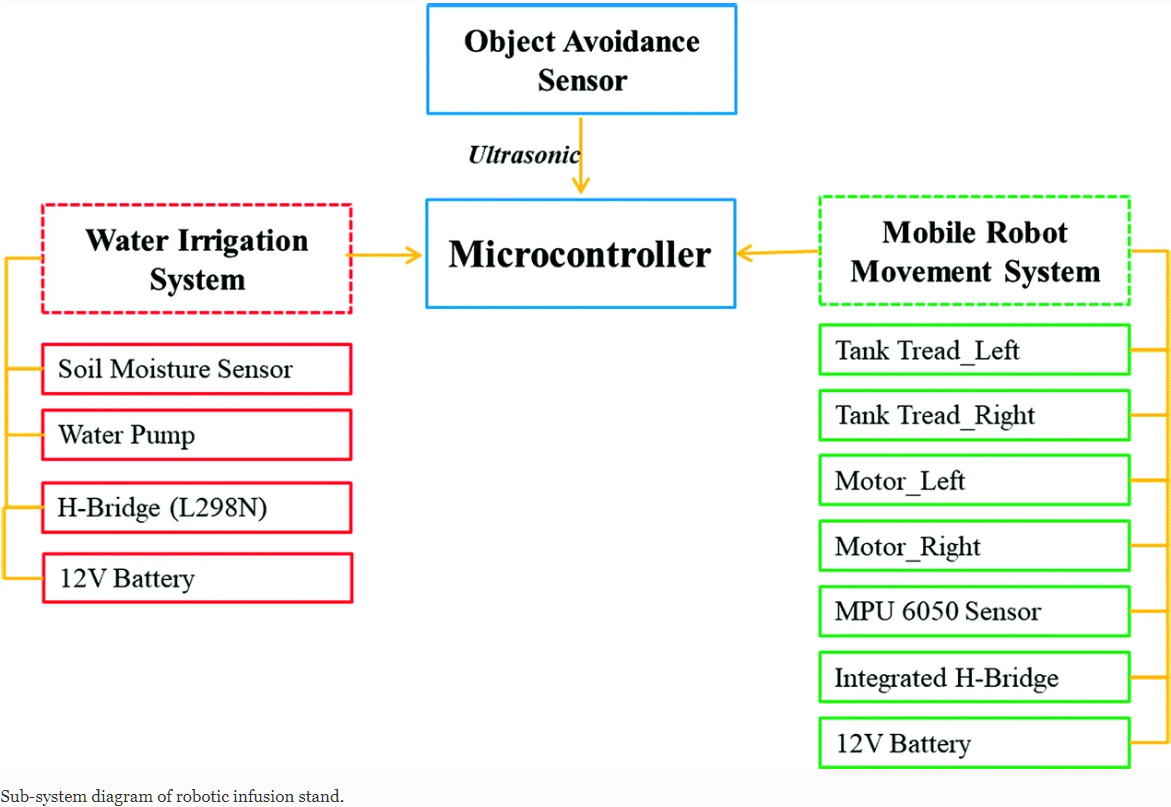

Optimal Proportional Integral Derivative (PID) Controller Design for Smart Irrigation Mobile Robot with Soil Moisture Sensor

Uncertainty on the condition of the weather always give a major headache to the agricultural industry as the cultivated plant that is grown on a large scale commercially rely on the condition of the weather. Therefore, to reduce the interdependency on the weather itself, a recommendation to develop a prototypic mobile robot for smart irrigation is submitted. Smart irrigation system is an essential tool from yield point of view and scarcity of the water. This smart irrigation system adopts a soil moisture sensor to measure the moisture content of the soil and automatically provide a signal to

Study of Energy Harvesters for Wearable Devices

Energy harvesting was and still an important point of research. Batteries have been utilized for a long time, but they are now not compatible with the downsizing of technology. Also, their need to be recharged and changed periodically is not very desirable, therefore over the years energy harvesting from the environment and the human body have been investigated. Three energy harvesting methods which are the Piezoelectric energy harvesters, the Enzymatic Biofuel cells, and Triboelectric nanogenerators (TENGs) are being discussed in the paper. Although Biofuel cells have been investigated for a

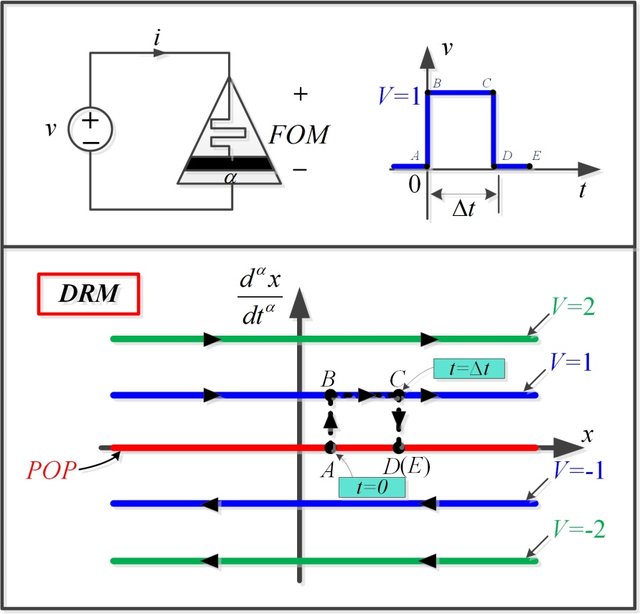

Study of fractional flux-controlled memristor emulator connections

In this paper, the series and parallel connections of the fractional flux-controlled memristors are studied. Asymmetric I-V hysteresis with high I-V nonlinearity can be obtained from single fractional memristor as reported in literature. However, connecting different memristor emulators can convert the asymmetric hysteresis to symmetric one and maintaining the high I-V nonlinearity to be used in some memristor devices. The proposed circuits have been analyzed mathematically to study the effect of changing the frequency and fractional power. Different cases have been verified on PSpice using

Stochastic modeling of mushroom—waveguide photodetectors

Waveguide photodetectors (WGPDs) are one of the promising candidates to solve the tradeoff between the quantum efficiency and the transit time in the surface illuminated photodiodes where the lightwave is incident laterally perpendicular to the direction of the flow of generated carriers, enhancing both high speed and quantum efficiency. In Mushroom-WGPDs, the performance degradation due its parasitic capacitance and the load resistance is overcome due to the mesa mushroom structure. Inaccuracies in the dimensions of’Mushroom-WGPDs due to the fabrication affect its functionality and its

Multiple Pinch-Off Points in Memristive Equations: Analysis and Experiments

Pinched hysteresis behavior is considered evidence of the existence of the memristive element. Recently, the multi-lobes (more than two) behavior has been discovered in some memristive devices. In this paper, a fractional-order flux/voltage-controlled memristive model is introduced that is able to develop multiple symmetric and asymmetric pinch-off points. Generalized closed-form expressions for the necessary conditions of multiple pinch-off points existence are derived in addition to the coordinates of the pinch-off points in the I-V plane. Closed-form expressions for the minimum and maximum

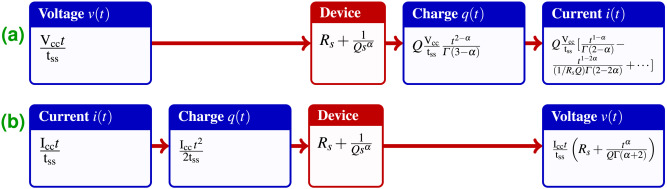

Supercapacitor reciprocity and response to linear current and voltage ramps

The focus in supercapacitor research typically falls into one of two categories: (i) the rational design and engineering of electrode materials and electrolyte formulation to achieve high performance devices at competitive costs, and (ii) the modeling of their resulting behavior in response to constant-current charging/discharging, cyclic voltammetry or impedance spectroscopy. However, less work has been dedicated to new ways for charging these devices. In this work we show that charging a supercapacitor, modeled as a constant phase element with a series resistor, using a linear voltage ramp

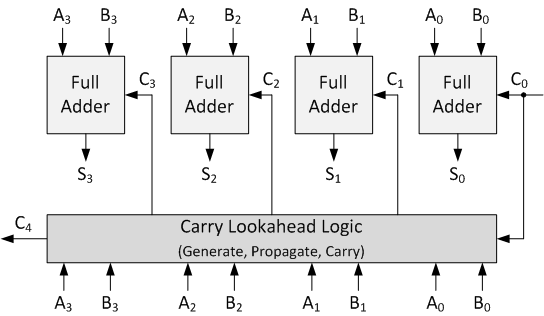

N-digits ternary carry lookahead adder design

Carry lookahead adders (CLAs) are extensively used in digital circuits due to their logarithmic computational time (O(log n)) compared to linear computational time(O(n)) in the ripple carry adders. In this paper, two design approaches for N-digits ternary logic CLA based on K-map and threshold logic methods are proposed in addtion to their realization using CNTFETs only and memristor with CNTFETs. Finally, 4-bit ternary CLA is presented. A comparison and tradeoffs among the proposed designs are presented in terms of the delay and the area. The comparison shows that the transistor-only-based

Supercapacitor discharge under constant resistance, constant current and constant power loads

Supercapacitors, which are now widely used as power sources in various applications, are discharged with one of the following three basic discharge modes: a constant current load, a constant resistance load or a constant power load. A constant current load is one which varies its internal resistance to achieve a constant current regardless of the applied voltage. For the constant resistance case, it results in a change of power as the voltage level changes. And for a constant power load, the load varies its impedance as the input voltage changes in order to keep the power constant. However

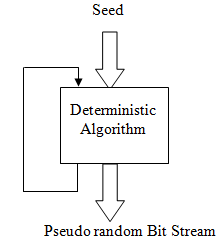

Multiplierless chaotic Pseudo random number generators

This paper presents a multiplierless based FPGA implementation for six different chaotic Pseudo Random Number Generators (PRNGs) that are based on: Chua, modified Lorenz, modified Rössler, Frequency Dependent Negative Resistor (FDNR) oscillator, and other two systems that are modelled using the simple jerk equation. These chosen systems can be employed in high speed applications because they don't utilize any hardware multiplier. The proposed PRNGs have been implemented using VHDL, synthesized on Xilinx, using the FPGA: XC5VLX50T, and tested using the NIST statistical suite. Furthermore, a

Pagination

- Previous page ‹‹

- Page 9

- Next page ››